Firmware middleware professional developers

Who are firmware middleware professional developers?

firmware professional developers are engineers who design and develop software for a specific chipset using c or assembly language they write api that can talk to upper layers like middleware and also talk to the chipset via cpu registers.

Do you need firmware middleware professional developers for your projects then get in touch with use to discuss your project details

Device tree

It presumably abandons saying that equipment programmers were energized when the Raspberry Pi 4 was declared, however it wasn’t on the grounds that there was another section into the universally adored line of Linux SBCs. The new Pi offered various convincing equipment updates, including an installed PCI-Express interface. The main issue was that the PCIe interface was devoted to the USB 3.0 regulator; yet that isn’t anything a hot-air revamp station couldn’t fix.

We’ve recently observed consistent given programmers eliminate the USB 3.0 regulator on the Pi 4 to interface different PCIe gadgets with to some degree blended outcomes, however [Colin Riley] has increased present expectations by effectively getting a PCIe multiplier board working with the minute Linux PC. While there are still some product wrinkles to work out, the outcomes are promising and he as of now has a couple of gadgets working.

Getting that first PCIe port added to the Pi 4 is now genuinely surely knew, so [Colin] simply needed to follow the model set by programmers, for example, [Tomasz Mloduchowski]. Sufficiently sure, when he stopped the port multiplier board in (after a touch of what he alludes to as “proficient squirming”), the suitable section appeared in lspci.

Yet, there was an issue. While the port multiplier board was perceived by the bit, nothing he connected to it appeared. Checking the part logs, he discovered messages identifying with transport clashes, and one that appeared to be particularly significant: “gadgets behind extension are unusable on the grounds that [bus 02] can’t be alloted for them”. To make a long story short, things being what they are, the Raspbian part is explicitly designed to just permit a solitary PCI transport.

Luckily, it’s a simple fix once you recognize what the issue is. Utilizing the “Gadget Tree Compiler” device, [Colin] had the option to alter the Raspbian Device Tree document and change the PCI “transport run” variable from <0x0 0x1> to <0x0 0xff>. From that point, it was simply a question of connecting various gadgets and seeing what works. Basic things, for example, USB regulators were no issue, yet getting ARM Linux uphold for the NVIDIA GTX 1060 he attempted should be a point for one more day.

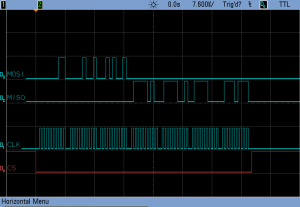

SPI

The DSPI is a completely configurable SPI ace/slave gadget, which permits client to design extremity and period of sequential clock signal SCK. It permits the microcontroller to speak with sequential fringe gadgets. It is likewise equipped for interprocessor interchanges in a multi-ace framework. A sequential clock line (SCK) synchronizes moving and examining of the data on the two free sequential information lines. DSPI information are at the same time communicated and got. What’s the most significant, it’s an innovation autonomous plan that can be actualized in an assortment of cycle technologies.The DSPI framework is adaptable enough to interface straightforwardly with various standard item peripherals from a few producers. It very well may be arranged as an ace or a slave gadget, with information rates as high as CLK/4. Clock control rationale permits a choice of clock extremity and a decision of two essentially unique timing conventions to oblige most accessible coordinated sequential fringe gadgets. At the point when the SPI is designed as an ace, programming chooses one of eight distinctive bit rates for the sequential clock.The DSPI naturally drive chose by SSCR (Slave Select Control Register) slave yields (SS7O – SS0O) and address SPI slave gadget to trade sequentially moved information. What’s more significant, mistake discovery rationale is incorporated to help interprocessor correspondences. A compose impact locator shows, when an endeavor is made, to compose information to the sequential move register, while an exchange is in progress. A numerous ace mode-flaw identifier naturally impairs DSPI yield drivers, if more than one SPI gadgets all the while endeavors to become transport master.What does it mean for you? The DSPI is completely adjustable, which implies that we convey it custom fitted to your arrangement and necessities. There is no compelling reason to pay extra for not utilized highlights and squandered silicon. It incorporates completely computerized testbench with complete arrangement of tests, permitting simple bundle approval at each phase of SoC configuration stream.

Linux kernel

An investigation of the Linux bit, directly from its initially submit on 17 September 1991 to 2 August this year, shows that it has had in excess of 20,000 givers in those 29 years.

The principal part, linux-0.01.tar.Z, had 88 records and 10,239 lines of code and ran on one design, i3868. Today, the v5.8 discharge has 69,325 documents and 28,442,673 lines of code (which compares to 110,354,844 tokens), and runs on in excess of 30 significant designs.

These, and a lot of other fascinating realities about the bit, have been gathered in the examination which is named 2020 Linux Kernel History Report and delivered a month ago.

Insights about portion advancement used to be at first delivered by engineer Jonathan Corbet, who runs the Linux Weekly News site. The Linux Foundation at that point encouraged the work and today there are in any event 12 individuals chipping away at it.

The examination additionally takes a gander at the three particular periods of advancement: the principal, when there was no form control framework set up, the second when BitKeeper was utilized, and the third when Git had its spot.

Read more about this